Croc

Croc

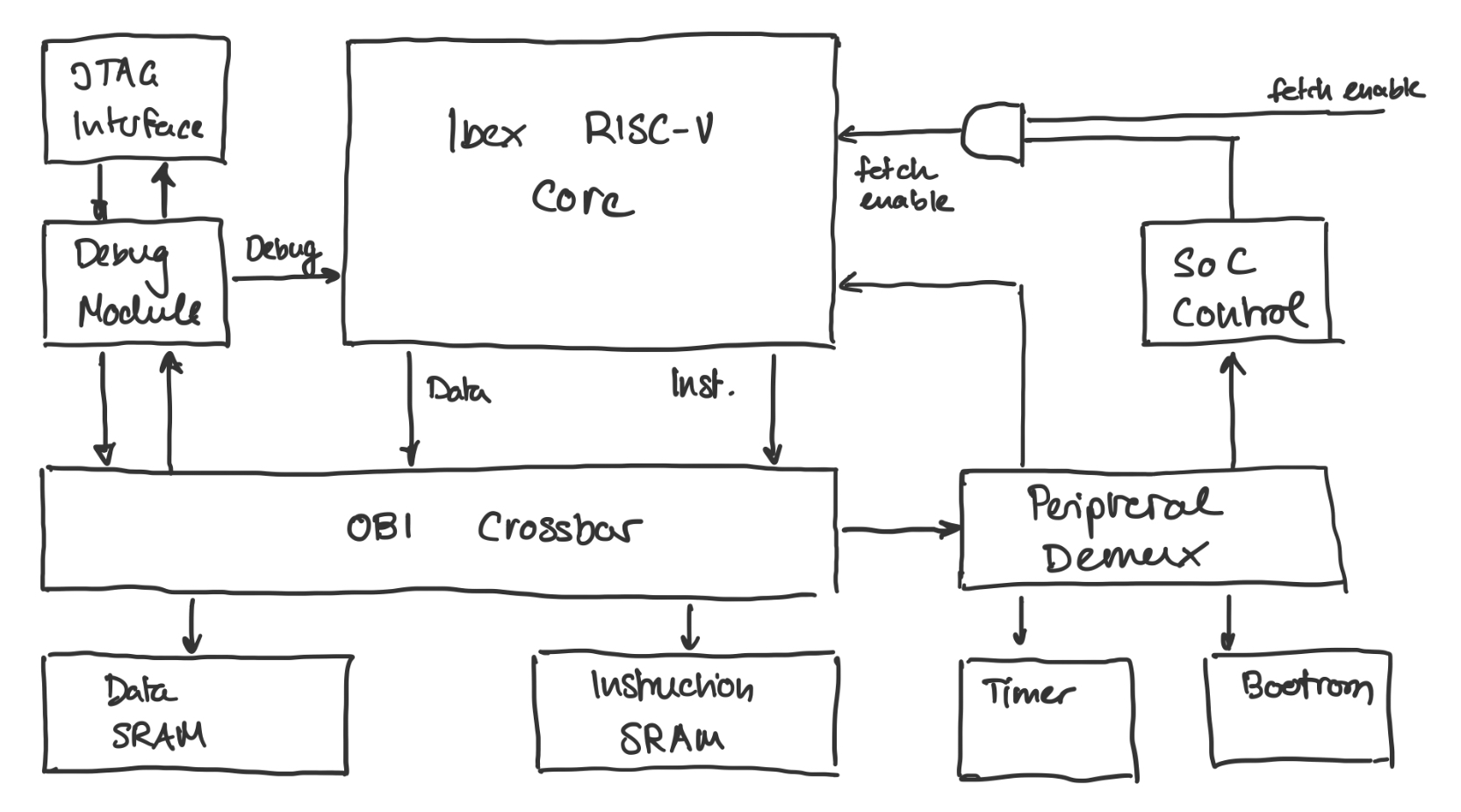

Our open source SoC template to be used for the VLSI Exercises.

Introduction

We believe that an important part of learning is by playing around with a meaningful design. We have designed Croc to represent a modern SoC while keeping it simple enough so that most steps required in the VLSI Exercises can be completed within a reasonable amount of time on an average computer.

Over the years our open source offerings have been improved to allow them be used in may different projects. While this flexibility is great, it has also added a fair amount of complexity and configuration options into the codebases. With Croc we have simplified these and pruned the code from many of its parameters and have included all parts of the design in one repository.

Download

Croc, like all our other offerings, is available using a permissive license under GitHub

Components

We maintain Croc as a monorepo, but it consists of the following distinct main components

- Ibex: 32bit RISC-V processor, originally developed as zeroriscy within PULP, now maintained by LowRISC

- OBI Open Bus Interface maintained by the OpenHW group

The VLSI pages are part of the open source VLSI design course offered by the Integrated Systems Laboratory of ETH Zürich, by Luca Benini and Frank K. Gürkaynak. See full list of contributors.