VLSI: Difference between revisions

From Antalya

No edit summary |

No edit summary |

||

| Line 6: | Line 6: | ||

</ul> | </ul> | ||

</div> | </div> | ||

---- | |||

=== Image trials === | |||

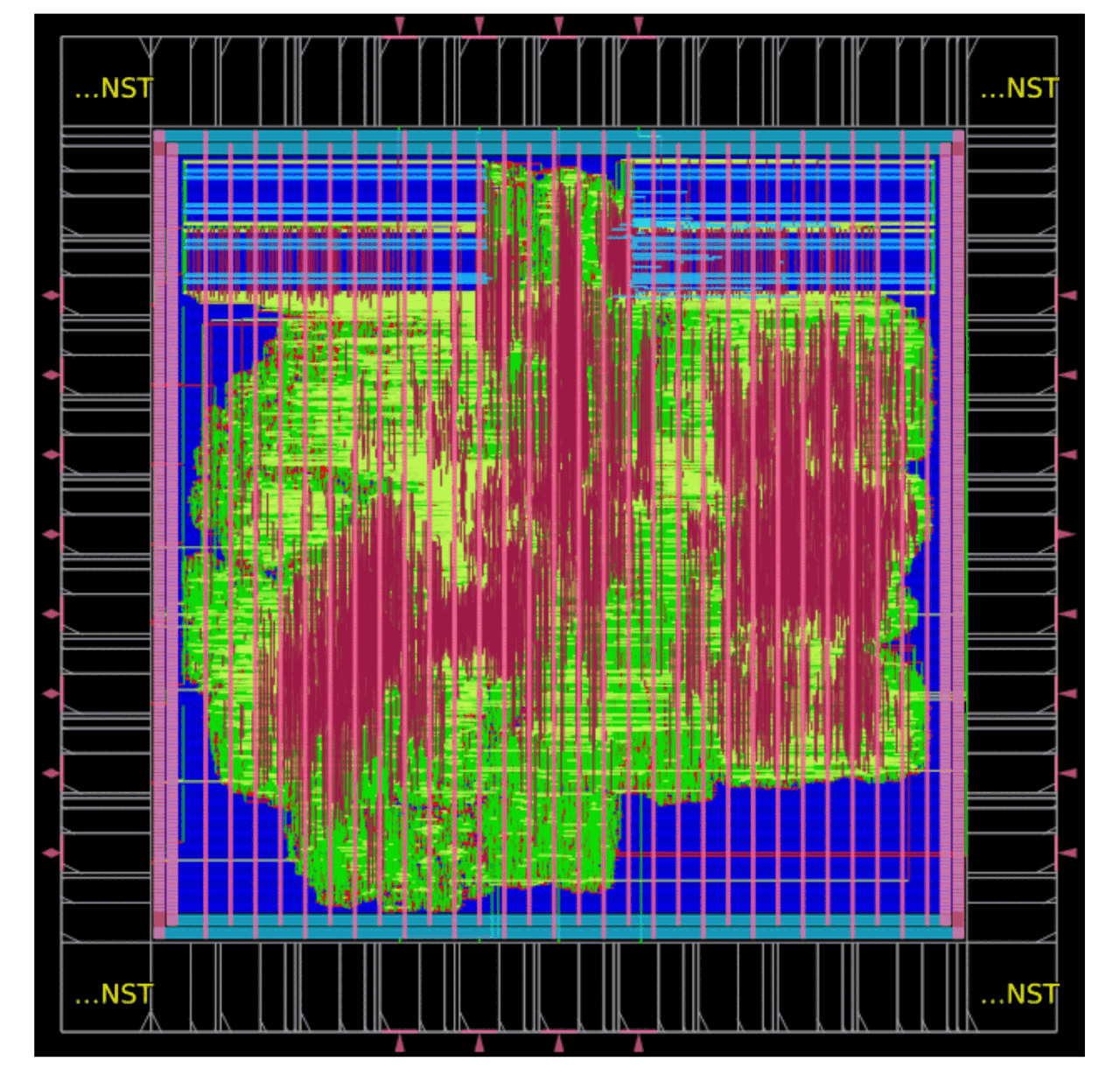

{{VLSIfigure|ex2_openroad_croc.png|This is an example caption}} | |||

---- | ---- | ||

===Code example=== | ===Code example=== | ||

Revision as of 07:11, 13 August 2024

Open Source VLSI Design

These pages support the VLSI design activities at ETH Zürich relying on mainly open source EDA design tools.

Image trials

Code example

module test (input logic data_in_i,

input logic clk_ci,

input logic rst_ni,

output logic [7:0] output_o);

// body of module

always_ff (@posedge clk_ci, @negedge rst_ni) begin

if (rst_ni ==1'b0) begin //active_low reset

output_o = 8'b0;

end else begin

output_o = {8{data_in_i}};

end

end

endmodule

Some inline code always_ff or more prominent press Shift-F

Some row examples

Learning goals

Example text

Header

Some quick example text to build on the card title and make up the bulk of the card's content.

Uneven distribution

of columns

The VLSI pages are part of the open source VLSI design course offered by the Integrated Systems Laboratory of ETH Zürich, by Luca Benini and Frank K. Gürkaynak. See full list of contributors.